引言

目前,发光二极管(light emitting diode,LED) 显示 屏具有色彩鲜艳、图像清晰、亮度高、驱动电压低、功 耗小、耐震动、价格低廉和使用寿命长等优势[1]。 LED 显示图像的非均匀度是衡量 LED 显示屏显示质量的 指标,非均匀度过高,会导致 LED 显示图像出现明暗 不均的情况,影响显示效果,降低 LED 显示屏的显示 质量[2-4]。 因此,对于 LED 模块的亮度和灰度不一致 问题,已提出很多的非均匀度校正方法,普遍使用的 是基于 CCD ( charge-coupled device ) 的 校 正 技 术[5]。根据 CCD 采集到的亮度信息,通过一系列算法,得到 用于校正的系数矩阵,然后把校正系数和显示图像的 灰度信息在 LED 显示屏上表现出来,从而实现非均匀度的校正。

由模块拼接而成的 LED 显示屏,在拼接过程中模块的位置在垂直或者水平方向会发生偏离理想位置 的情况形成位置畸变[6]。 由于此时 LED 显示屏是一 个畸变的光学系统,所以显示图像会产生失真和灰度 畸变,而原因就是非均匀度过高。 因此必须对 LED 显 示屏进行适当的灰度校正,消 除 畸 变[7]。 本 文 在 FPGA 中进行非均匀度的校正处理,基于 Cyclone Ⅱ系 列的芯片 EP2C8Q208C 来实现由于灰度畸变而进行的 LED 屏显示图像非均匀度校正,并对整个系统进行 了仿真。

1 LED 显示屏的非均匀度校正

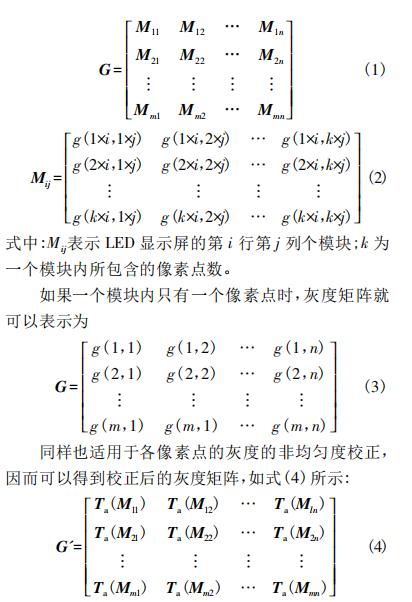

LED 显示屏创建的图像在特定条件下工作于不 同环境中时,显示画面时常会出现太亮或太暗的极端 情况,因此需要对 LED 显示系统灵活地进行灰度畸变 调节[8]。 首先,需定义一个用于表征显示像素点灰度 值的灰度矩阵 G,如式( 1) 所示。

该方法是以模块为单位对像素点灰度的非均匀 度进行校正的,即以相同的校正方式对同一模块内的 像素点进行校正,此方法并未真正实现对灰度值的逐 点校正。当模块内只有一个像素点的时候,如式( 5) 所示的校正后得到的灰度校正公式,此时才是真正意 义上实现了对灰度值的逐点校正,因此,仅当模块内 只有一个像素点时,才能实现逐点校正。

将式( 6) 代入式( 5) 即可得到各像素点的灰度值 修正结果,如式( 7) 所示:

G'相当于一张对 LED 显示屏做灰度畸变校正的 系数表,LED 显示屏将该矩阵中的信息和显示图像的 灰度信息同时显现出来。具体的灰度校正过程为: 将 各像素点的灰度校正结果 G'和显示图像各像素点的 灰度信息对应元素相乘,即可完成灰度校正。

2 系统硬件实现

LED 显示屏的数据来源是计算机显示卡的 DVI 接口,它有红、绿、蓝各 8 位共 24 位彩色图像数据,包 括使能数据、同步和混合数据,这些数据与显示屏是 完全同步的[9]。本文介绍的基于 FPGA 的 Look -Up Table 技术,具有高速精准的优点,例 如 系 统 使 用 EP2C8Q208C 的访问时间为 10 ns,理论上可以实现 100M 的查表速度,在 2 个时钟周期以后,查找表便可 输出查找到的结果[10]。

2.1 校正系统构成

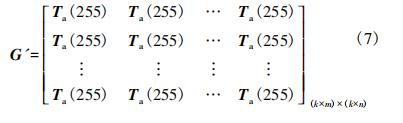

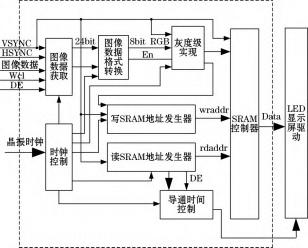

本设计是 LED 显示系统的一部分,系统框图见图 1。 该系统从计算机显示卡的DVI 接口输出图像信号,包括3 路的 RGB 信号,经过 DVI 解码电路变成 3 路 8 位数字信 号。然后在 FPGA 中进行非均匀度的校正处理,之后将 校正后的图像数字信号输入到驱动控制电路,最后由驱 动控制 LED 显示屏,使其更好地显示图像。

图 1 校正系统的框图

在 FPGA 中的具体实现过程为: 首先使用 Altera 自带的 IP 核,实例化 3 个数据宽度为 8 bit,数据深度 为 256 的双端口 RAM 作为查找表。系统启动时,初 始化模块首先从外部 EEPROM 中读出 256 个配置数 据,初始化 RAM 查找表。初始化完成后,灰度变换模块 将 24 bit RGB 数据分离成 3 个 8 bit 数据作为 RAM 地 址,读出数据作为转换后的灰度值。当需要修改值时, 通过 PC 机软件生成新的校正表,然后通过串口发送到FPGA,在灰度变换模块的控制下将数据写入 RAM。

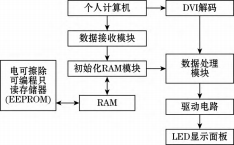

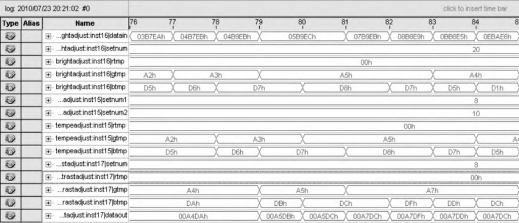

将整个系统包括校正模块构成的顶层文件经过 Quartus Ⅰ全编绎,并得到 SignalTap Ⅱ中对灰度校正 模块调试的时序图,如图 2 所示,从时序图中看出初始 化模块从 RAM 中读出数据写入 EEPROM 中。3 个RAM 中存放的是相同的校正数据,所以初始化模块可以同时对 3 个 RAM 初始化,在从RAM 中读出配置数据时也只需要其中一个 RAM 中的值。通过本方法结 合 PC 机软件可以实现上述的灰度畸变的非均匀度校正。

图 2 灰度校正模块时序

2.2 FPGA 数据处理

本论文设计使用的是 Cyclone Ⅱ 系 列 的 芯 片 EP2C8Q208C,QuartusⅡ是综合性的可编程逻辑器件 的开发软件,内嵌有综合器及仿真器,能够实现从开 发输入到配置硬件内部逻辑元素的整个开发流程[11]。图 3 为 FPGA 控制系统内部结构,当图像数据传送到 FPGA 内部,需进行一系列的数 据处理才能输出给 LED 显示,主要有 : 图像数据的获取、对获取的数据进 行格式转换、实现三基色 256 灰度级的调节、灰度畸变 校正和输出 LED 显示的控制信号。

图 3 FPGA 控制系统内部结构

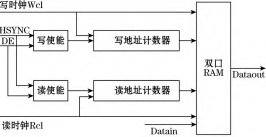

采用双端口 RAM 形式的图像数据获取模块,在 获取图像数据后对其进行暂时的存储。 双端口 RAM 每个端口能够独立地采用时钟信号边沿触发方式读 取图像数据。 图 4 为图像数据获取模块的原理图,当DE 和 HSYNC 同时有效时,RAN 计数器开始工作,此时 RAM 将保持与从解码电路输出的像素频率相同的频率读入数据。 在双端口读写下一行图像存储数据之前需保证本次读写已完成。 在将图像数据输出给驱动 LED 显示屏之前需将从解码电路输出的并行 24位图像数据信号转换为红、蓝、绿 3路并行数据信号。在数据转换完成后还需要用横向写入、纵向读取的方式实现图像数据权值的读写,将图像中8位数据按其不同的权值对应不同占空比,确保实现红、蓝、绿三基色256 灰度级。

图 4 图像数据获取原理图

读 SRAM 模块是通过灰度级的存储实现模块数据 的输出,RAM 按从低位到高位的顺序输出内部数据,因 此,SARM 按行存储每个像素点的三基色信号,按列读

取输出给 LED 显示屏的驱动信号。 在场同步信号上升 沿到来时,各计数器进行变量初始化,SRAM 时钟上升 沿到来时,开始读取数据,输出高电平,计数器的输出值 作为地址输出。 当 SRAM 内部数据读取完之后,将输出 低电平的使能信号给下级并将计数器清零。

在导通时间的控制中,若将图像的数据周期 256

等分,LED 的点亮时间就是每份最低权值对应的导通 时间,从而得到最低导通时间。 当图像数据从 SRAM 中读出后开始启动计数器,在时钟信号的控制下,图 像数据通过移位寄存器输出给 LED 驱动信号,在输出 过程中移位信号需要比使能信号延迟一个周期,以确 保能够读取出全部的图像信号,并且为了避免信号的 覆盖,需要暂存输出的数据。 当读出图像数据到锁存 器中时,本模块会输出一个使能,使得锁存器中的数 据按特定权值驱动 LED,移位信号延迟一个周期后,回到稳定状态输出下一帧图像,循环执行下去。

时钟控制模块主要功能是利用锁相环(PLL) 为系 统各模块提供时钟信号,时钟信号由锁相环内部的自 振荡器产生,该信号作为反馈传送到相频检测电路, 该电路会通过比较器确定时钟信号大小,从而调节输 出的时钟周期。

3 实验结果及分析

3.1 亮度分布对比

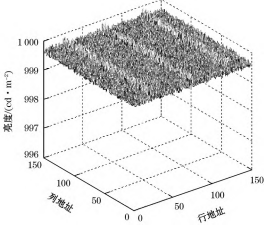

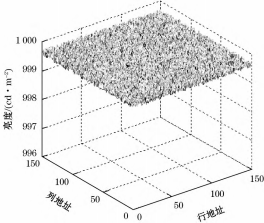

对一块分辨率为 128 pixel×128 pixel 的 LED 显示 屏进行显示图像的非均匀度校正,该显示屏每个显示

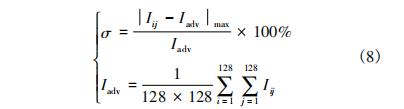

模块对应一个像素点。 依据 LED 显示屏的亮度分布 情况,同时根据《LED 显示屏测试方法》SJ /T 11281— 2003 中提供 的 计 算 LED 显 示 图像的非均匀度的方 法,通过式(8) 可以得出校正前和采用本文所述非均 匀度校正后亮度分布图,两者对比即可验证本文设计 方法的有效性[12] :

式中 : Iadv为 LED 显示屏的平均亮度; Iij为第 i 行第 j 列 的像素点的亮度[13]。

校正前、校正后 LED 显示屏亮度分布如图 5、图 6 所示。 图 5 中,由于 LED 显示图像的非均匀度过高, 显示图像产生了失真和一定的灰度畸变。 图 6 中,经 过非均匀度校正后的图像畸变消失。 计算结果如表 1 所示。 由表 1 可知,经过校正,显示图像的非均匀度由 原来的 67.9% 降低到 0.96%,因此该非均匀度校正方 法是有效的。

3.2 FPGA 开发板仿真验证

本文所采 用 的 FPGA 开 发 板 是 EP2C8Q208C 芯 片,由于条件限制,仅将灰度级实现模块、导通时间控 制模块和 SRAM 模块下载到开发板进行验证,将已有 的计算机中的图像经数据转换后存储到 FPGA 内部存储单元,经过模块的数据处理将结果显示在开发板的 液晶屏上。

图 7 为验证 FPGA 开发板的有效性设计显示的图 案,将程序输入 Quartus Ⅱ软件进行编译后无错误,可 见模块设计的逻辑是无错误的,将程序下载到开发板 后,如图 8 所示,可见开发板液晶显示器依次显示图 7 所示的图 片,即 基 于 FPGA 非均匀度校正方法是可行的。

图 5 校正前 LED 显示屏亮度分布

图 6 校正后 LED 显示屏亮度分布

图 7 显示的图片

图 8 开发板的显示结果

4 结论

本文提出了一种基于 FPGA 的 LED 显示图像的 非均匀度校正方法。 首先,解决了由于 LED 显示屏在 拼接过程中出现的 LED 显示图像灰度畸变而造成的 非均匀度过高的问题,通过分析得到了校正 LED 显示 屏的灰度校正矩阵,其次,给出了一种基于 FPGA 的 Look-Up Table 技术的非均匀度校正的设计方法及系 统构成,实现了在 FPGA 内部进行非均匀度校正的功 能。 采 用 Cyclone Ⅱ系 列 的 芯 片 EP2C8Q208C 来 实 现,并对整个系统进行了仿真。 结果表明,基于FPGA 的 Look-Up Table 技术的非均匀度校正方法能够有效地消除图像的灰度畸变。

免责声明:凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。